### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{\circ} \times 9^{\circ}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

# EXPLORING QUALITY-OF-SERVICE ISSUES IN NETWORK INTERFACE DESIGN

by

Atri Indiresan

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 1997

**Doctoral Committee:**

\$

Professor Kang G. Shin, Chair Assistant Professor Peter M. Chen Associate Professor Farnam Jahanian Professor Toby J. Teorey Assistant Professor Kimberley M. Wasserman

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### UMI Number: 9811104

Copyright 1997 by Indiresan, Atri

All rights reserved.

UMI Microform 9811104 Copyright 1997, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

**UMI** 300 North Zeeb Road Ann Arbor, MI 48103

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

© <u>Atri Indiresan</u> 1997 All Rights Reserved

---

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

To my parents and Rohini.

₽ ₽ ₽ ₽ ₽

----

### ACKNOWLEDGEMENTS

I would like to thank everyone who supported and assisted me during my academic career at the University of Michigan. First and foremost, I would like to thank my advisor, Professor Kang G. Shin for his encouragement and support during my Ph.D. program. He allowed me to pursue my own research interests, and was always available to discuss various problems and provide feedback. In addition to his role as an academic mentor, he was always concerned about his students as individuals. I would like to thank Professors Peter Chen, Farnam Jahanian, Toby Teorey and Kimberly Wasserman for serving on my thesis committee and for their advice and support. A note of thanks to Professors Stuart Sechrest and Anthony Woo for serving on my thesis proposal committee. I would like to extend special thanks to Professors Farnam Jahanian and John Meyer for discussions on research, and their encouragement and friendship.

I would like to gratefully acknowledge the National Science Foundation and the Office of Naval Research for providing financial support during the course of my graduate program.

Many people have contributed to this dissertation in one way or the other. I had a very fruitful collaboration with Ashish Mehra, and our work together greatly contributed to this thesis. I would like to thank everyone who collaborated with me and contributed to the development of HARTS: Dilip Kandlur, Jim Dolter, Harold Rosenberg, Seungjae Han and Jaehyun Park.

The city of Ann Arbor and the University of Michigan gave me some of the best years of my life, and it is with deep regrets that I take my leave. It is a beautiful and vibrant place, but most important of all, it is where I met many wonderful people. I treasure the friendship of fellow students in the RTCL, including Ashish Mehra, Chao-ju Hou, Dan Kiskis, Dilip Kandlur, Harold Rosenberg, Jennifer Rexford and Sushil Birla. I will always remember Beverly J. Monaghan, the RTCL administrative assistant, for her friendship and many enjoyable conversations. Karen Liska, the EECS graduate secretary, always went beyond the call of duty to be helpful. I cherish the friendship of the people whom I met during my stay in Ann Arbor. I wish to thank John Lynn, Melora Goosey, S. Mohan, Raghu Mani, Sushila Subramanian, Vidyullata Waghulde and many others for their friendship and hospitality.

1

The Shotokan Karate of Michigan has been an extremely important part of my life in Ann Arbor. While I learned a lot from everyone in the dojo, my special thanks to John Teramoto and to my instructors, Dean Askounis, Ravindra Prasad and Adam Liebowitz. Sergej Roytman, Toni Guzzardo, Sandeep Rao, Mary Prasad, Michael Sandoval, Tracy McComb, Tina Yee and many others – thank you for the wonderful times we had together, both in and out of the dojo.

My parents, Jayalakshmi and P.V. Indiresan, always taught me the importance of knowledge, and encouraged me to acquire it and use it wisely. Their example and their Ph.D.'s have always been an inspiration to me. I would like to thank them and my sisters, Nitya and Gowri, for their love, patience and understanding over the long years of my Ph.D.

The last few months of my Ph.D. were the hardest, but my wife, Rohini, made it all possible through her love and encouragement. She also spent endless hours reading multiple drafts of my thesis and helping me improve the presentation. I truly owe her a debt of gratitude for all that she has done for me.

## TABLE OF CONTENTS

i

| DEDICATIO   | N                                                         |

|-------------|-----------------------------------------------------------|

| ACKNOWLE    | DGEMENTS iii                                              |

| LIST OF TAI | BLES viii                                                 |

| LIST OF FIG | URES ix                                                   |

| ABSTRACT    | xi                                                        |

| CHAPTERS    |                                                           |

| 1 INTR      | <b>ODUCTION</b>                                           |

| 1.1         | Scope of the Research                                     |

| 1.2         | Contributions of the Dissertation                         |

| 1.3         | Outline of the Dissertation                               |

| 2 COM       | MUNICATION SUBSYSTEM DESIGN                               |

| 2.1         | Real-time Communication                                   |

| 2.2         | Implementation of Real-time Communication Services 11     |

| 2.3         | Network Adapter Design 14                                 |

|             | 2.3.1 Adapter Design and Evaluation Techniques            |

|             | 2.3.2 The Case for Device Emulation 18                    |

| 3 DESIC     | GN TRADEOFFS IN IMPLEMENTING REAL-TIME CHANNELS 21        |

| 3.1         | The Experimentation Platform                              |

|             | 3.1.1 Hardware                                            |

|             | 3.1.2 Software                                            |

|             | 3.1.3 Baseline System Measurements 27                     |

| 3.2         | Implementation of Real-time Channels                      |

|             | 3.2.1 Real-time Channel API 28                            |

|             | 3.2.2 Channel Establishment and Teardown                  |

|             | <b>3.2.3 Data Transfer</b> 31                             |

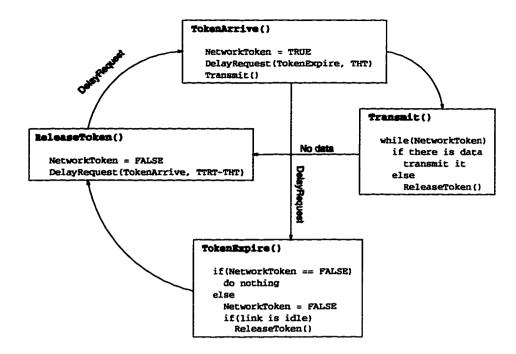

|             | <b>3.2.4 Run-time Link Scheduler</b>                      |

| 3.3         | Influence of Network Adapter Characteristics              |

|             | 3.3.1 CIM Performance Characteristics and Implications 35 |

|             | 3.3.2 Desirable Adapter Features                          |

| 3.4         | Overhead of Protocol Processing                           |

|             | 3.4.1 Data-transfer Optimizations                         |

|   |            | 3.4.2 Software Overhead and Protocol Thread Scheduling 40          |

|---|------------|--------------------------------------------------------------------|

|   |            | 3.4.2.1 Fragmentation and Link Scheduling Overhead 40              |

|   |            | 3.4.2.2 Scheduling Protocol Threads                                |

|   |            | 3.4.3 End-to-end Performance 43                                    |

|   | 3.5        | Effectiveness of Link Access Scheduling                            |

|   |            | 3.5.1 Outline of Experiments                                       |

|   |            | 3.5.2 Effect of Best-effort Traffic Load on Real-time Traffic 45   |

|   |            | 3.5.3 Effect of Burstiness and Message Size on Delay Guarantees 46 |

|   | 3.6        | Conclusions                                                        |

|   |            | END: A NETWORK ADAPTER DESIGN TOOL                                 |

| 4 |            |                                                                    |

|   | 4.1        |                                                                    |

|   | 4.2        |                                                                    |

|   |            |                                                                    |

|   |            | 4.2.2 Adapter Internals                                            |

|   |            | 4.2.3 Adapter-Network Interface                                    |

|   | 4.3        | END Emulation Architecture                                         |

|   |            | 4.3.1 Host View of the Network 57                                  |

|   |            | 4.3.2 Emulator Components 58                                       |

|   |            | 4.3.3 Implementation                                               |

|   |            | 4.3.4 Emulator Operation 62                                        |

|   |            | 4.3.5 Two-way Communication Across the "Network" 64                |

|   |            | <b>4.3.6 Reception Modeling</b>                                    |

|   | 4.4        | Platform Considerations                                            |

|   |            | 4.4.1 System Capacity Analysis                                     |

|   |            | 4.4.2 Overcoming the Limitations of the Platform 66                |

|   | 4.5        | END Software Implementation                                        |

|   | 4.6        | Related Work                                                       |

|   | 4.7        | Conclusions                                                        |

| 5 | ADAF       | TER DESIGN USING END: A CASE STUDY                                 |

| Ŭ | 5.1        | Emulating the Ancor CIM 250 using END 72                           |

|   | 0.1        | 5.1.1 Ancor CIM 250                                                |

|   |            | 5.1.2 CIM Functional Model                                         |

|   |            | 5.1.3 CIM Performance Emulation                                    |

|   |            | 5.1.3.1 Arriving at an Accurate Base Model                         |

|   |            | 5.1.3.2 Accounting for Concurrency and Contention 79               |

|   |            | 5.1.3.3 Equivalence of the CIM and the END Model 81                |

|   | 5.2        | CIM Transmission Analysis and Optimization                         |

|   | 0.2        | 5.2.1 Reducing the Host-Adapter Interface Overhead                 |

|   |            | 5.2.2 Exploiting Increased Concurrency                             |

|   |            | 5.2.3 Performance of the Improved CIM                              |

|   | 5.3        | Discussion                                                         |

|   | 5.3<br>5.4 | Discussion                                                         |

|   | J.4        |                                                                    |

| 6 | QUAL       | ITY-OF-SERVICE ISSUES IN ADAPTER DESIGN 88                         |

|   | 6.1        | A QoS-sensitive Communication Subsystem                            |

|   | 6.2        | Research Goals and Approach 91                                     |

| 6.3       | Point-to-point Network Model                          | 92       |

|-----------|-------------------------------------------------------|----------|

|           | 6.3.1 Experimental Configuration                      | 93       |

|           | 6.3.2 Evaluation Workload                             | 94       |

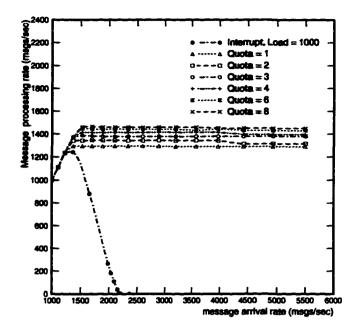

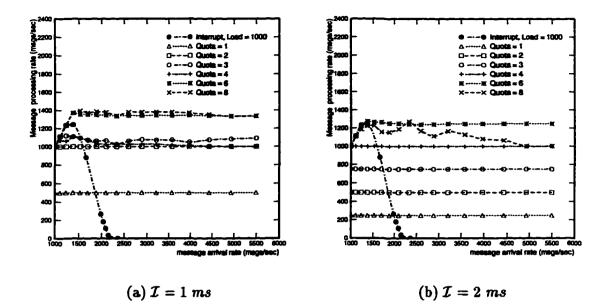

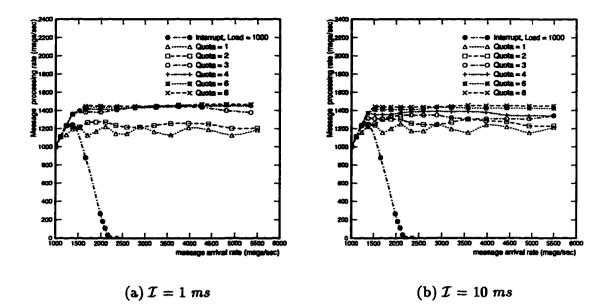

|           | 6.3.3 Best-effort Performance                         | 94       |

|           | 6.3.4 Real-time Performance                           | 96       |

|           | 6.3.5 Discussion                                      | 96       |

| 6.4       | Shared Network Model                                  | 98       |

|           | 6.4.1 Network Model                                   | 99       |

|           | 6.4.2 Experimental Configuration                      | 99       |

|           | 6.4.3 Evaluation Workload                             | 01       |

|           | 6.4.4 Host and Emulator QoS Support                   | 02       |

|           | 6.4.5 Effect of CPU Capacity and Scheduling on QoS 10 | 05       |

| 6.5       | <b>Conclusions</b>                                    | 08       |

|           |                                                       | 10       |

|           |                                                       | 10       |

| 7.1       |                                                       | 11<br>14 |

| 7.2       |                                                       |          |

|           | ·····                                                 | 15       |

|           |                                                       | 16       |

|           |                                                       | 18       |

| 7.3       |                                                       | 20       |

|           |                                                       | 21       |

|           | ······································                | 21       |

|           |                                                       | 23       |

|           |                                                       | 24       |

|           |                                                       | 25       |

|           |                                                       | 26       |

|           | 7.3.7 Discussion                                      | 27       |

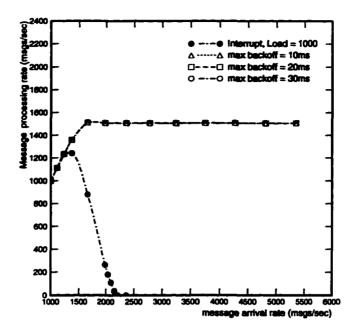

| 7.4       | Multiple Interrupt Sources                            | 28       |

|           | 7.4.1 Host-based Solutions                            | 28       |

|           | 7.4.2 Adapter-based Solutions                         | 29       |

|           | 7.4.3 Experimental Evaluation                         | 30       |

|           | 7.4.4 Discussion                                      | 32       |

| 7.5       | Conclusions                                           | 35       |

| 0 0000    |                                                       | )¢       |

|           |                                                       | 36<br>26 |

| 8.1       |                                                       | 36       |

| 8.2       | Future Work                                           | 39       |

| BIBLIOGRA | PHY                                                   | 41       |

~

•

# LIST OF TABLES

#### Table

ì

| 3.1 | Baseline system performance                                                   | 27          |

|-----|-------------------------------------------------------------------------------|-------------|

| 3.2 | The real-time channel API                                                     | 29          |

| 4.1 | Configurable components of END.                                               | 60          |

| 4.2 | Portability of END.                                                           | 69          |

| 5.1 | Important CIM parameters                                                      | 77          |

| 6.1 | Experimental configurations and parameters                                    | 94          |

| 6.2 | Workload used for evaluating the point-to-point network                       | 95          |

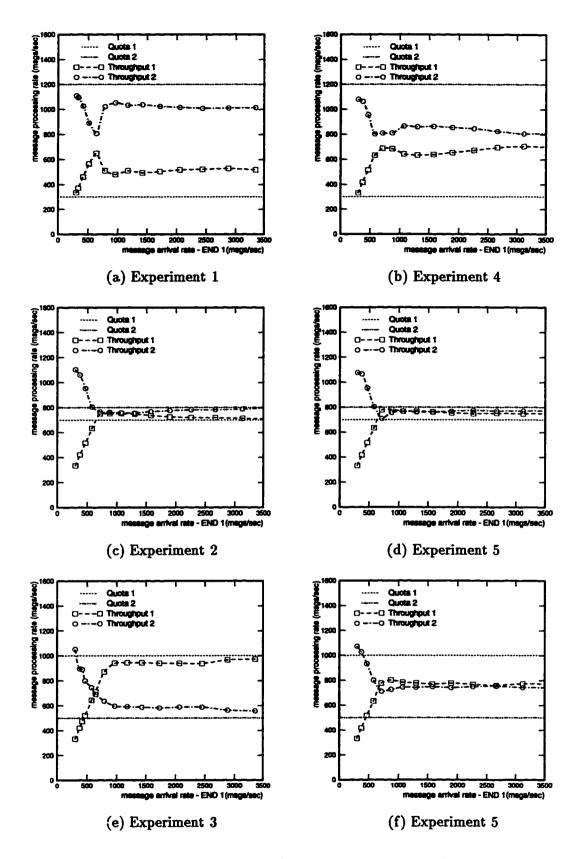

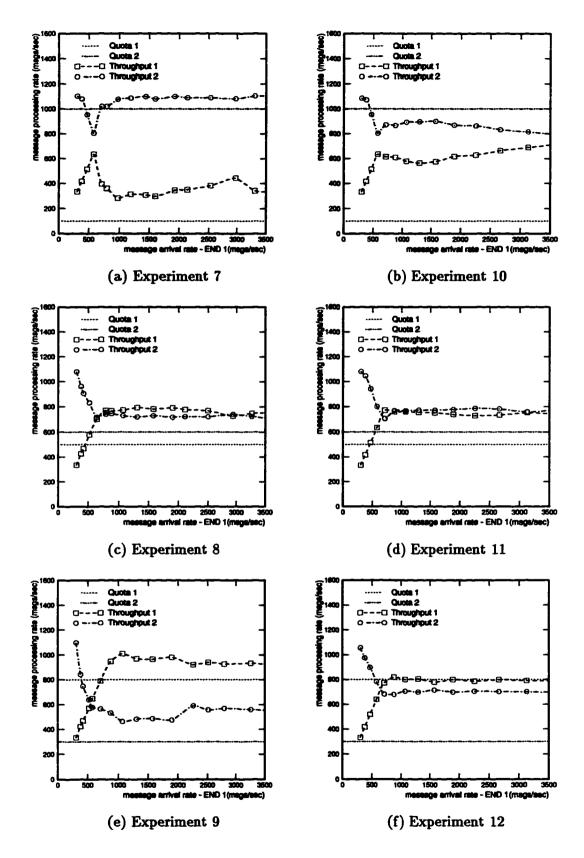

| 6.3 | Workload used for evaluating the shared network                               | 101         |

| 6.4 | Traffic characterization of sample MPEG traces from [86]                      | 1 <b>02</b> |

| 7.1 | Adapter control commands                                                      | 117         |

| 7.2 | Important system parameters                                                   | 121         |

| 7.3 | Experimental configurations: $I_{min} = 1 ms$ , $I_{max} = 20 ms$ . Note that |             |

|     | $Quota = \frac{Q}{2 \times I_{max}}$ .                                        | 131         |

# LIST OF FIGURES

## Figure

ŝ

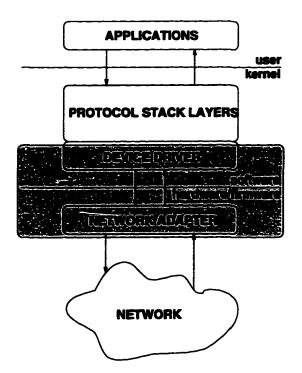

| 1.1        | Typical communication subsystem at end hosts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

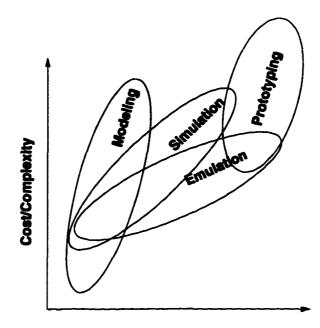

| 2.1        | Performance evaluation techniques and tradeoffs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .7 |

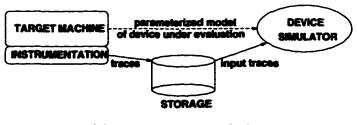

| 2.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .9 |

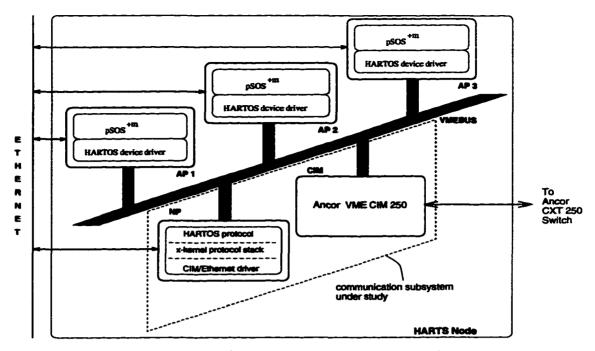

| 3.1        | Architecture of each HARTS node 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24 |

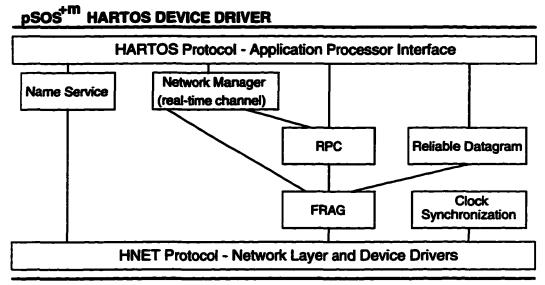

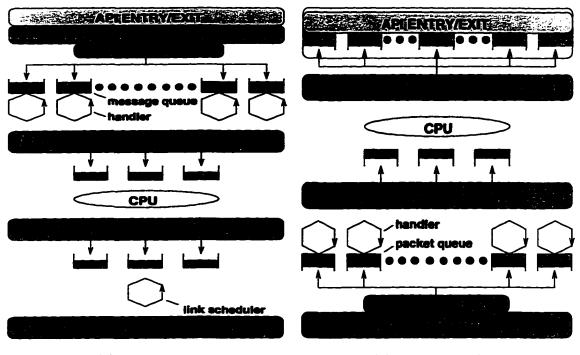

| 3.2        | The <i>x</i> -kernel protocol stack in HARTOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26 |

| 3.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81 |

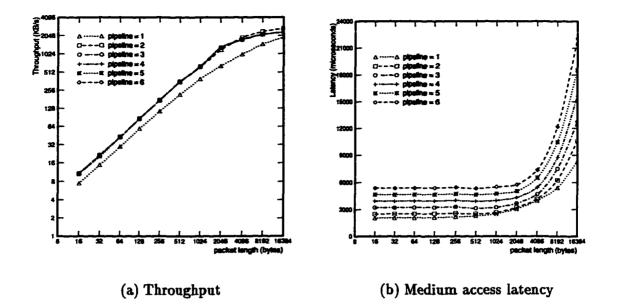

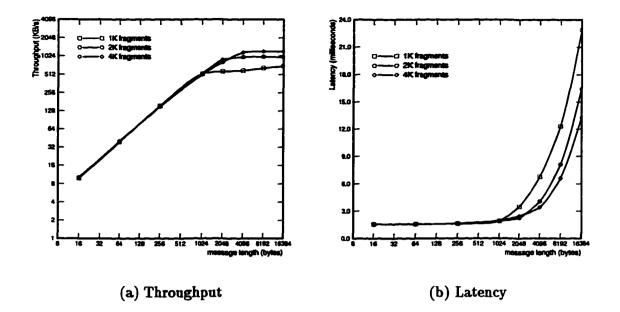

| 3.4        | Performance of the Ancor CIM 250 network adapter. Note that in (a), both                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|            | axes have log scales, and in (b), only the x-axis has a log scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6  |

| 3.5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .1 |

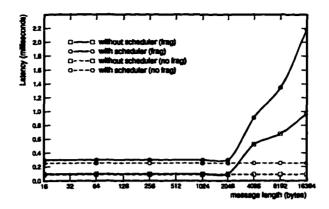

| 3.6        | Protocol processing performance with fragmentation (with CIM) 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4  |

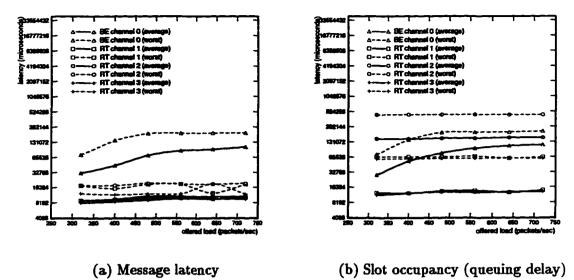

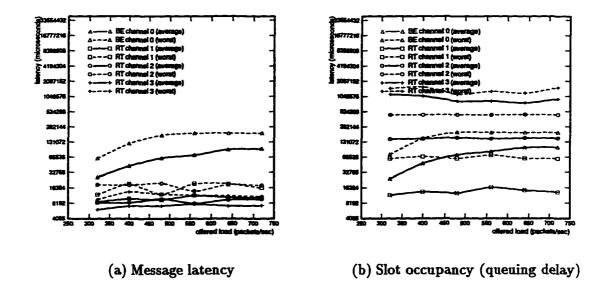

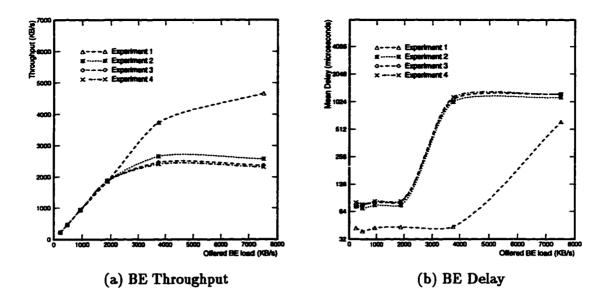

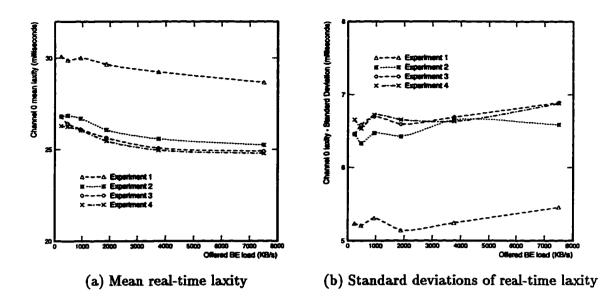

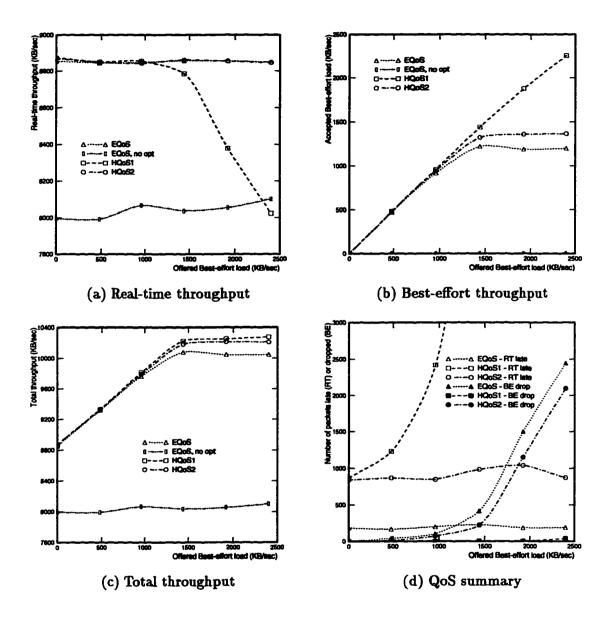

| 3.7        | Well-behaved real-time channels with variable best-effort load 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5  |

| 3.8        | Ill-behaved real-time channels with variable best-effort load 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6  |

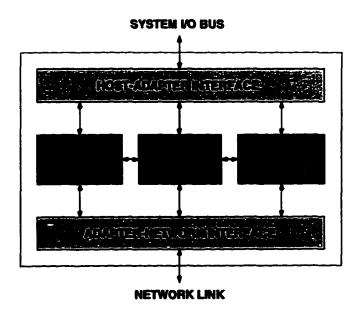

| 4.1        | Generic network adapter architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1  |

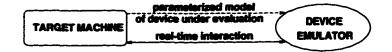

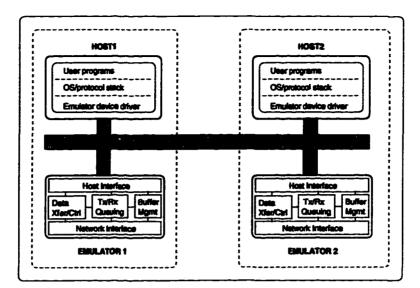

| 4.2        | END-based device emulation architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8  |

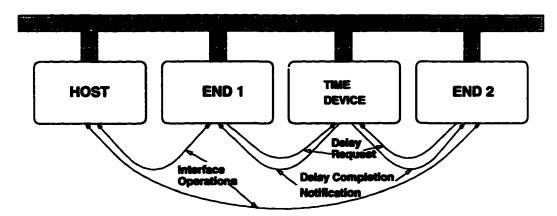

| 4.3        | Emulator system configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9  |

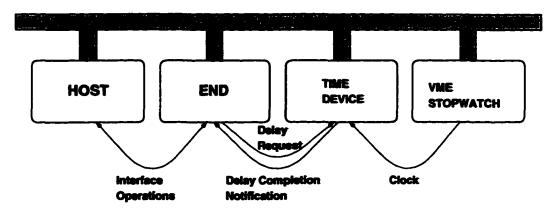

| 4.4        | Transmission emulation for <i>n</i> -stage adapter operation 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3  |

| 5.1        | Host-adapter interaction for data transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4  |

| 5.2        | Host-adapter interaction for data reception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5  |

| 5.3        | Outline of END model for transmission on the CIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6  |

| 5.4        | Outline of END model for reception on the CIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6  |

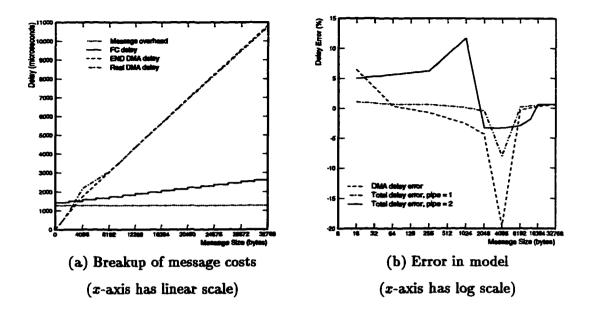

| 5.5        | Sources of delay in the model and their accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9  |

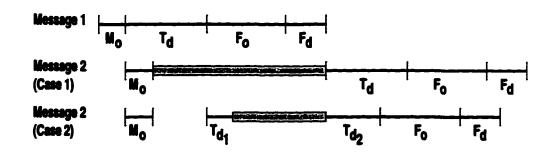

| 5.6        | Inter-message overlap during CIM transmissions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0  |

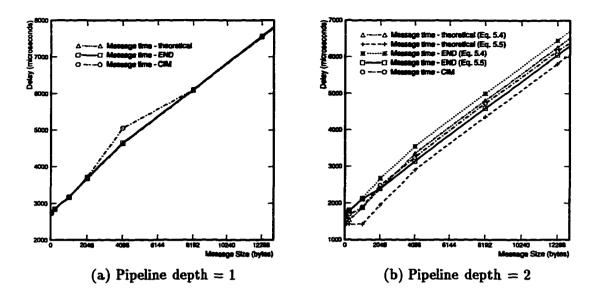

| 5.7        | Theoretical and measured mean message times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  |

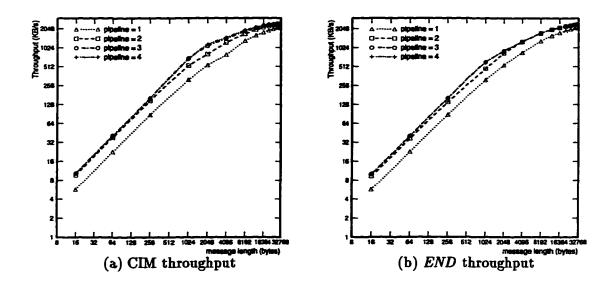

| 5.8        | Comparison of CIM and END's transmission throughput. Note that the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|            | graph uses a log-log scale, and throughput increases by as much as 50%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|            | when mentione hit and action to mention of the second                                                                                                                                                                                                                                             | 2  |

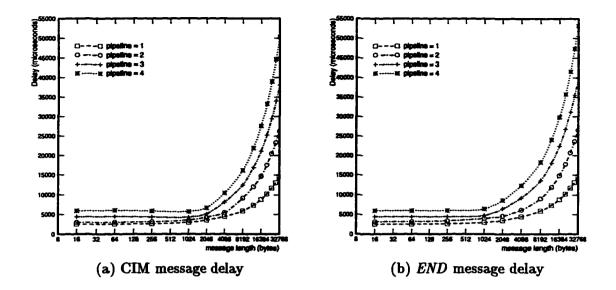

| <b>5.9</b> | Compation of Olive and Stop of themation and Jack Stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3  |

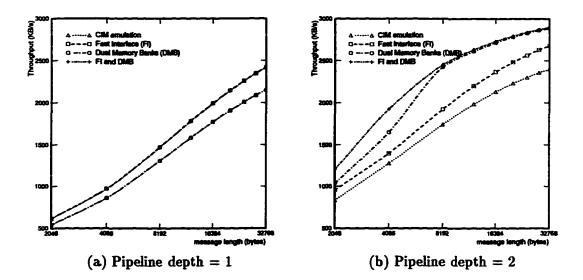

| 5.10       | Transmission throughput for improved CIM models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

| 6.1        | QoS-sensitive communication architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 6.2        | 2007 energeneralized for the for the former and the | 6  |